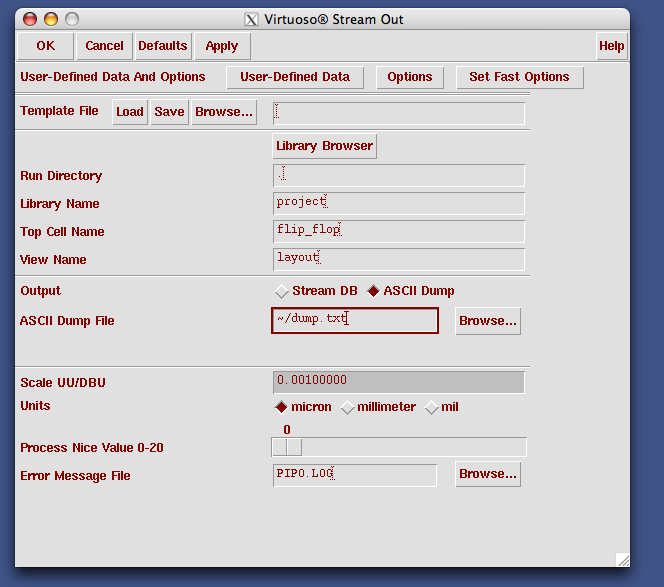

By appending a wire label with a '!',the label becomes global. In this tutorial, we'll just call them VDD! and VSS!ġ. To find out the names the library uses for the power nets, look at any layout of the basic cell (e.x. Set the following items, and Click OK.Ĭase 1: If your design has transistor level schematic beneath the top level schematic, please follow the procedure below:įor your simulation to work properly, make sure you have specified the power nets (VDD, VSS, and GND). Set the following items, and Click OK.ĭ) A new window appears.

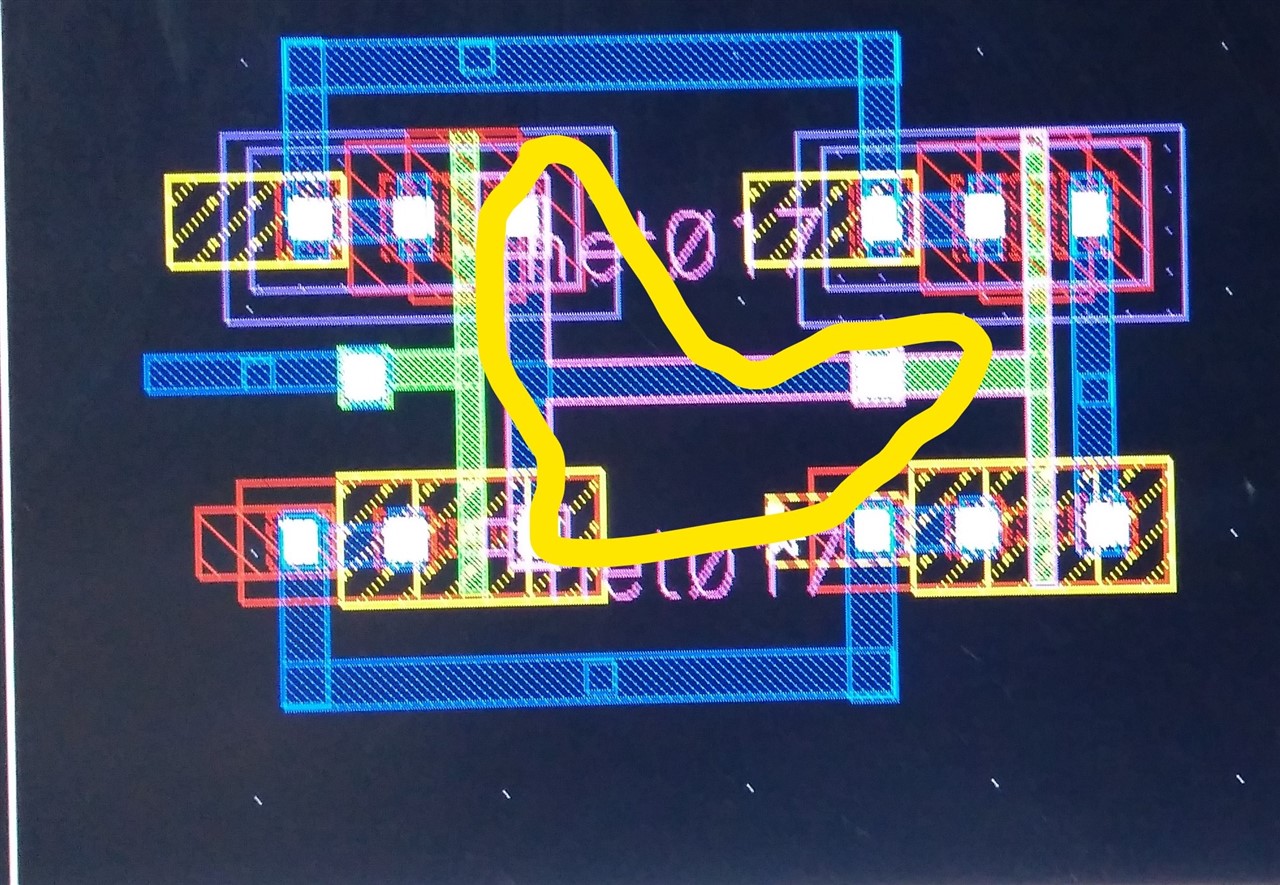

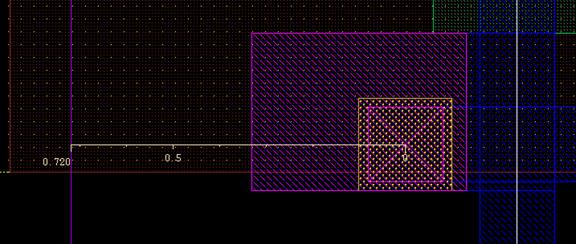

If you don't have any of them, refer to previous sections, Schematic Entry with Composer, and Layout with Virtuoso for MOSIS Library for the layout.ī) A new window appears. You also have to have a switch-level schematic diagram (view name: schematic) of every gate used in the gate level schematic diagram in MOSIS library. Otherwise, refer to Setting UP Your Unix Environment.īefore you start, you have to have a gate-level schematic diagram (view name: schematic) and a layout (view name: layout) of a multiplexer in MOSIS library. At this point, you should have set up the environment. This tutorial shows how to perform layout-versus-schematic (LVS) check using a multiplexer. Authors: Jeannette Djigbenou, Jia Fei, and Meenatchi Jagasivamani

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed